Tìm thấy 1 việc làm đang tuyển dụng

Design Verification Senior / Staff Engineer

Thông tin cơ bản

Mức lương:

Thỏa thuận

Chức vụ:

Nhân viên

Ngày đăng tuyển:

10/12/2024

Hạn nộp hồ sơ:

26/01/2025

Hình thức:

FULL_TIME

Kinh nghiệm:

5 - 6 năm

Số lượng:

1

Giới tính:

Không yêu cầu

Nghề nghiệp

Ngành

About The Opportunity

We are Synopsys Solution Group, and we are proud to be at the heart of the innovations that impact the world and change the way people live. Everything you need to enable innovation from Our Technology, Your Innovation is what we make at Synopsys. This opportunity offers much more than just an engineering job, this is from Synopsys Solution Group - the top IP provider in the world, where the best IPs with the broadest portfolio and the most advanced technology are created.

If you’re ready to excel, innovate, and pursue a passion in ASIC Design Verification for IP, Subsystem or SoC, we’d like to welcome you to our newly created Subsystem Verification Team in Ho Chi Minh city, Vietnam. We are looking for Design Verification talents of various levels: Design Verification Engineers, Leads and Managers. With your expertise, together with the industry most talented professionals in the team, empowered by Synopsys EDA ecosystem, you are fueling the new era of Era of Pervasive Intelligence by offering high-speed silicon-proven interface IP solutions in the latest process technology for the most cutting-edge industry vertical including Artificial intelligence, Autonomous Vehicles, High-Performance Compute, Cloud, 5G Mobile and the IoT etc. IPs and subsystems you make will be integrated into tens of millions of SoCs that are used by billions of people.

You will be joining a true global team that has personality, enthusiasm and a fun culture with diversity. You will have all the support you need to grow and develop with us. No matter where you are in your career, the experience and expertise you grow here will put you miles ahead in the career advancement and open the path to all possibilities.

Responsibilities:

Inclusion and Diversity are important to us. Synopsys considers all applicants for employment without regard to race, color, religion, national origin, gender, sexual orientation, gender identity, age, military veteran status, or disability.

We are Synopsys Solution Group, and we are proud to be at the heart of the innovations that impact the world and change the way people live. Everything you need to enable innovation from Our Technology, Your Innovation is what we make at Synopsys. This opportunity offers much more than just an engineering job, this is from Synopsys Solution Group - the top IP provider in the world, where the best IPs with the broadest portfolio and the most advanced technology are created.

If you’re ready to excel, innovate, and pursue a passion in ASIC Design Verification for IP, Subsystem or SoC, we’d like to welcome you to our newly created Subsystem Verification Team in Ho Chi Minh city, Vietnam. We are looking for Design Verification talents of various levels: Design Verification Engineers, Leads and Managers. With your expertise, together with the industry most talented professionals in the team, empowered by Synopsys EDA ecosystem, you are fueling the new era of Era of Pervasive Intelligence by offering high-speed silicon-proven interface IP solutions in the latest process technology for the most cutting-edge industry vertical including Artificial intelligence, Autonomous Vehicles, High-Performance Compute, Cloud, 5G Mobile and the IoT etc. IPs and subsystems you make will be integrated into tens of millions of SoCs that are used by billions of people.

You will be joining a true global team that has personality, enthusiasm and a fun culture with diversity. You will have all the support you need to grow and develop with us. No matter where you are in your career, the experience and expertise you grow here will put you miles ahead in the career advancement and open the path to all possibilities.

Responsibilities:

- Define verification plans and build verification environments for block/sub-system level designs using Verilog, System Verilog and UVM.

- Write test cases, checkers, and coverage that implement the verification test plan.

- Apply advanced verification techniques like constrained random generation, functional coverage, assertions, and formal verification.

- Work closely with RTL designers and other parts of our global verification team to debug failures.

- Bachelor or Master degree in EE or CS.

- 5+ years of experience in design verification in the industry.

- Knowledge of one or more protocols such as AMBA, PCI-Express, CXL, UCIe, Ethernet, HBM, DDR…

- Knowledge of industry-standard simulators, revision control systems, and regression systems.

- Experience of RTL verification using coverage driven verification techniques

- Experience in developing System Verilog, UVM or similar HDL based test environments.

- Programming skills such as HDL, Verilog, System Verilog, C, Perl, Python.

- Good analytical, oral, and written communication skills.

- Self-motivated, proactive team player.

Inclusion and Diversity are important to us. Synopsys considers all applicants for employment without regard to race, color, religion, national origin, gender, sexual orientation, gender identity, age, military veteran status, or disability.

Khu vực

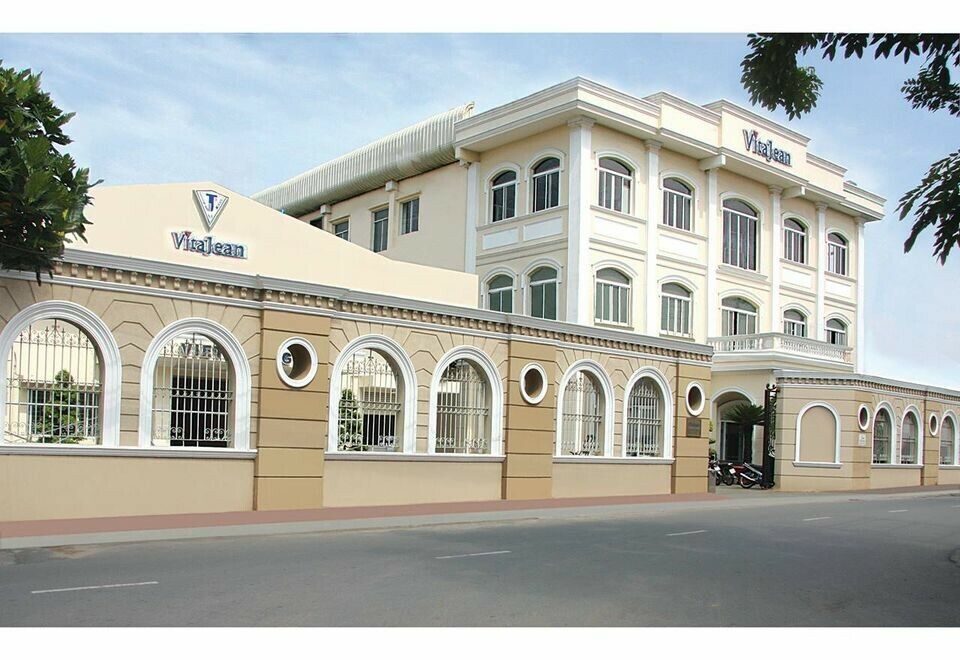

Việt Thắng Jean

Xem trang công ty

Quy mô:

500 - 1.000 nhân viên

Địa điểm:

38 Quang Trung, Phường Hiệp Phú, Thành phố Thủ Đức, Thành phố Hồ Chí Minh, Việt Nam.

Công ty TNHH Việt Thắng Jean tên viết tắt là VITAJEAN được thành lập ngày 30/06/1988. VITAJEAN hoạt động trong lĩnh vực sản xuất và cung ứng sản phẩm thời trang Denim và Non-Denim cho các thị trường Việt Nam và quốc tế như Mỹ, EU, Nhật Bản, Hàn Quốc.

Chính sách bảo hiểm

- Được hưởng các chế độ bảo hiểm : BHYT, BHXH, BHTN

- Hưởng quyền lợi bảo hiểm 24/7

Các hoạt động ngoại khóa

- Du lịch hàng năm

- Team building theo quý

- Các hoạt động vui chơi, giải trí, ca hát thường xuyên

- Thể thao: Đá bóng, bóng chuyền,..

Lịch sử thành lập

- Công ty được thành lập năm 2003

Mission

Các mục tiêu chúng tôi đặt ra cho chương trình bền vững phản ánh trực tiếp tầm nhìn của chúng tôi về việc đảm bảo một tương lai lành mạnh hơn cho ngành

Review Việt Thắng Jean

1.0

2 review

10/06/2021

★

★

★

★

★

Nhân viên

tại Hồ Chí Minh

Công ty nợ lương, Môi trường làm việc không có hệ thống.

29/11/2021

★

★

★

★

★

PHP Developer

tại Hồ Chí Minh

công ty nợ lương

Những nghề phổ biến tại Việt Thắng Jean

Bạn làm việc tại Việt Thắng Jean? Chia sẻ kinh nghiệm của bạn

Việt Thắng Jean

Click để đánh giá

Tweet

Tweet

Facebook

Facebook

Copy Link

Copy Link